AI반도체연구회

AI-EDA: 인공지능 기반 반도체 설계 자동화

작성자

theise2

작성일

2023-06-29 15:17

조회

1833

POSTECH 전자전기공학과

강석형 (shkang@postech.ac.kr)

최근 ChatGPT 로 인해 AI(인공지능)에 대한 관심이 어느때 보다 높아지고 있습니다. 현재 AI의 눈부신 발전 속도를 보면, 반도체 설계 인력을 AI가 완전히 대체하게 될 날이 찾아올지도 모릅니다. 본 기고에서는 AI 기반 반도체 설계 자동화 분야의 연구 동향을 살펴 보고자 합니다.AI-EDA 란?

AI-EDA는 반도체 설계의 복잡한 문제들을 기계학습을 활용해 해결하는 방식으로 설계공간 탐색, 배치 및 배선 최적화, 설계 결과 예측, 회로 및 패턴 생성 등에 널리 활용될 수 있습니다. 구글은 딥러닝 용 AI 가속기인 TPU 설계에 강화학습을 적용하여 배치를 최적화 하였고, Synopsys 및 Cadence와 같은 EDA 업체들 역시 설계 생산성 향상을 위한 AI 기반 기술 개발에 박차를 가하고 있습니다.

반도체 설계 과정은 최상의 PPA(성능, 소비전력, 면적)를 얻어내기 위한 과정으로, 설계 과정에서 발생하는 경우의 수는 바둑보다 250배나 복잡합니다. 그럼 이렇게 복잡한 설계 과정의 효율성을 높이기 위해, 인공지능이 구체적으로 어떻게 활용되고 있을까요?

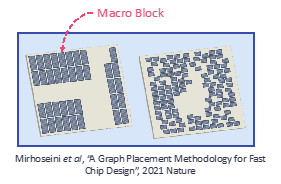

강화 학습을 이용한 매크로 블록 배치

구글은 2021년 Nature에서 인공지능 기반 반도체 설계 논문을 게재하였습니다. 해당 논문에서 제안한 방법은 블록들을 배치할 때마다 그에 따른 보상 (배선 길이와 혼잡도) 을 확인하고 다음 배치를 결정하는 강화학습 방식입니다. 특히, 주어진 회로를 인공신경망으로 학습하여 효율성을 향상시켰습니다. 제안된 방법은 반도체 설계 전문가들이 일주일에 걸쳐서 설계한 블록 배치를 단 6시간 만에 더 향상된 수준으로 완료할 수 있음을 보였습니다. 이는 아래 그림의 왼쪽처럼 규칙적인 배치가 아닌, 오른쪽처럼 사람이 생각해낼 수 없는 최적화된 배치를 인공지능 모델이 찾아낼 수 있었기 때문입니다.

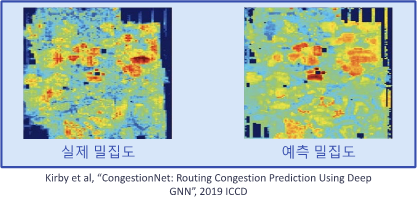

Physical Design 초기 결과 예측 (Earl-Stage Prediction)

반도체 설계 단계에서 배치 및 배선 (Place & Route) 과정은 가장 어려운 과정들 중 하나입니다. 오랜 시간을 기다려 완성된 레이아웃의 품질이 목표치에 미치지 못하거나 공정의 디자인 룰을 만족하지 못하는 경우, 반복되는 설계 수정이 필요합니다. 하지만, 설계를 진행하기 전 초기에 그 결과를 예측할 수 있다면 설계자들은 예측 결과에 기반하여 적절한 최적화로 설계 시간을 절약할 수 있을 것입니다.

아래 사진은 인공지능을 통해서 레이아웃 상의 배선 밀집도를 예측한 결과입니다. 설계가 끝난 레이아웃으로 모델을 학습시키고, 이를 새로운 설계 예측에 사용하였습니다.

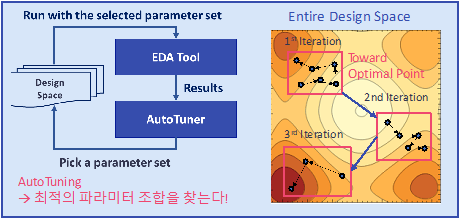

AutoTuning: 디자인 공간(Design Space) 최적화

EDA 툴은 수많은 설계 파라미터들을 가지고 있고, 이들은 셀 수 없을 정도로 많은 경우의 수 조합을 만들어 냅니다. 이렇게 만들어진 조합들을 디자인 공간(Design Space)이라고 부르는데, 지나치게 방대한 Design Space는 설계를 더욱 어렵고 오래 걸리게 만듭니다.

AutoTuning은 이러한 Design Space를 효율적으로 탐색하기 위한 방법으로, 사람의 경험에 의존하지 않고 자동화를 통해 최적의 파라미터 조합을 찾아내는 방법을 말합니다. 최근에는 베이지안 최적화와 강화 학습 등의 인공지능 기술들을 접목하여 높은 품질의 설계를 더욱 빠르게 얻어낼 수 있는 방법들이 활발히 연구되고 있습니다.

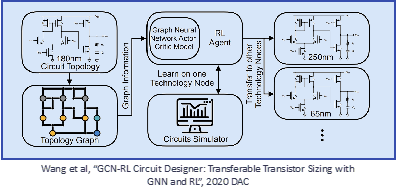

아날로그 회로 최적화

EDA Tool을 통해 많은 부분이 자동화가 되어있는 디지털 회로 설계와 달리 아날로그 회로 설계는 여전히 숙련된 전문가의 많은 경험과 노력을 요구합니다. 반도체 공정 미세화가 진행될수록 복잡한 소자 특성은 아날로그 회로 설계를 더욱 어렵게 만듭니다. 이러한 아날로그 설계의 한계를 극복하기 위해 인공지능 기반 설계 최적화 알고리즘들이 개발되고 있습니다.

아래 그림은 2020년 MIT에서 개발한 회로 설계 최적화 기법으로, Graph Neural Network (GNN) 과 강화 학습 및 전이 학습을 사용하여 설계 성능을 향상시켰습니다. 회로 모양을 그래프 형태로 학습하고, 소자 사이징 (Sizing) 으로 최적화 하여, 설계 전문가의 설계 대비 15%이상의 성능 향상을 가져 왔습니다.

그 외 적용 사례

지금까지 소개된 예시들 외에도 반도체 설계의 많은 분야에서 AI 기법들이 적용되고 있습니다. 소자의 동작 특성을 기계학습으로 모델링하여 엔지니어들이 수 년에 걸쳐 완성한 모델링 작업을 크게 단축시킬 수 있습니다. 또한, 리소그래피의 광학적 오차를 고려하여 최적의 마스크 패턴을 찾는 마스크 최적화 (Mask Optimization) 에서 적대적 생성 모델 (GANs) 을 이용하여 빠르게 패턴을 생성하고 높은 수율을 얻게 합니다. 이 외에도 공정 노드 별 설계 마이그레이션을 위한 자동화, 칩 테스트에서 커버리지 향상을 위한 테스트 패턴 생성 등 다양한 영역에 AI 기술을 사용할 수 있습니다.

마침말

나날이 증가하는 반도체 설계 복잡도와 설계 인력 부족에 대해, AI-EDA는 새로운 해결책으로 기대를 모으고 있습니다. 하지만, 아직은 AI 학습에 필요한 충분한 설계 데이터의 부재, 결과물에 대한 신뢰 문제, 그리고, 많은 컴퓨팅 자원 소모라는 한계도 분명 존재 합니다.

그럼에도, 언젠가는 ChatGPT와 같은 생성모델이 최적화된 RTL 코드를 작성하고, AI가 최적의 PPA를 가진 레이아웃을 자동으로 완성할 것입니다. 지금까지는 반도체 기술이 발전하며 AI의 발전을 이끌었다면, 앞으로는 AI가 직접 자기 두뇌인 반도체를 향상시키고 진화하는 것이지요. 이런 점에서, 인공지능 기반 반도체 설계 자동화는 앞으로 더욱 더 주목 받을 기술이라 생각합니다.

관련 논문

Mirhoseini et al., “A Graph Placement Methodology for Fast Chip Design”, Nature, 2021

Kirby et al., “CongestionNet: Routing Congestion Prediction Using Deep GNN”, Proc. ICCD 2019

Wang et al., “GCN-RL Circuit Designer: Transferable Transistor Sizing with GNN and RL”, Proc. DAC, 2020

Geng et al., "PTPT: Physical Design Tool Parameter Tuning via Multi-Objective Bayesian Optimization", IEEE Transactions on CAD, 2023

Kim et al., "Construction of Realistic Place-and-route Benchmarks for Machine Learning Applications”, IEEE Transactions on CAD, 2023

Lu et al, "RL-Sizer: VLSI Gate Sizing for Timing Optimization using Deep Reinforcement Learning", Proc. DAC, 2020.

전체 0